A.Dapat mengaplikasikan I2L

B.Memahami bagaimana prinsip kerja I2L

2. Alat dan Bahan [kembali]

3. Dasar teori [kembali]

Logika injeksi terintegrasi (I2L), juga dikenal sebagai logika injeksi arus, sangat sesuai untuk mengimplementasikan fungsi digital LSI dan VLSI dan merupakan pesaing dekat keluarga logika NMOS. Gambar 5.59 menunjukkan blok penyusun keluarga I2L dasar, yang merupakan transistor bipolar multikolektor dengan sumber arus yang menggerakkan basisnya. Transistor Q3 dan Q4 merupakan sumber arus. Besarnya arus tergantung pada R yang terhubung secara eksternal dan diterapkan + V. Arus ini juga dikenal sebagai arus injeksi, yang memberinya nama logika injeksi. Jika input A TINGGI, arus injeksi melalui Q3 mengalir melalui persimpangan basis-emitor Q1. Transistor Q1 jenuh dan kolektornya turun ke tegangan rendah, biasanya 50–100 mV. Ketika A RENDAH, arus injeksi disapu dari persimpangan basis-emitor Q1. Transistor Q1 menjadi terbuka dan arus injeksi melalui Q4 memenuhi Q2, sehingga potensial kolektor Q1 sama dengan tegangan saturasi basis-emitor dari Q2, biasanya 0.7V.

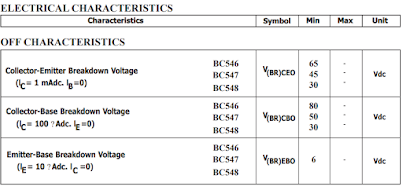

Kecepatan perangkat keluarga I2L adalah fungsi dari arus injeksi I dan meningkat seiring dengan peningkatan arus, karena arus yang lebih tinggi memungkinkan pengisian beban kapasitif yang lebih cepat yang ada pada basis transistor. Fitur arus injeksi yang dapat diprogram digunakan dalam keluarga I2L IC digital untuk memilih kecepatan yang diinginkan tergantung pada aplikasi yang dimaksudkan. Level logika '0' adalah VCE (sat.) Dari transistor penggerak (Q1 dalam kasus ini), dan level logika '1' adalah VBE (sat.) Dari transistor yang digerakkan (Q2 dalam kasus ini). Biasanya, level logika '0' dan logika '1' masing-masing adalah 0,1 dan 0,7V. Produk kecepatan-daya dari keluarga I2L biasanya di bawah 1pJ. Beberapa kolektor dari transistor yang berbeda dapat dihubungkan bersama untuk membentuk logika kabel.

Gambar 5.60 menunjukkan salah satu pengaturan tersebut, yang menggambarkan pembangkitan output OR dan NOR dari dua variabel logika A dan B.

4. Percobaan[kembali]

4.1 Prosedur Percobaan dan Rangkaian

1. siapkan alat dan bahan yang akan digunakan

5. Video

[kembali]

Video simulasi Gambar 5.58 dan 5.59

HTML disini!!!

Rangkaian Proteus 5.58 disini!!!

Rangkaian Proteus 5.59 disini!!!

Video disini!!!

Datasheet Resistor disini!!!

Datasheet Transistor NPN disini!!!

Datasheet Transistor PNP disini!!!

Tidak ada komentar:

Posting Komentar